# GEORG-AUGUST-UNIVERSITÄT GÖTTINGEN

# II. Physikalisches Institut

Implementation of an Electrical Read-Out System for Multi-Module Laboratory Tests of the ATLAS Pixel Detector

#### von

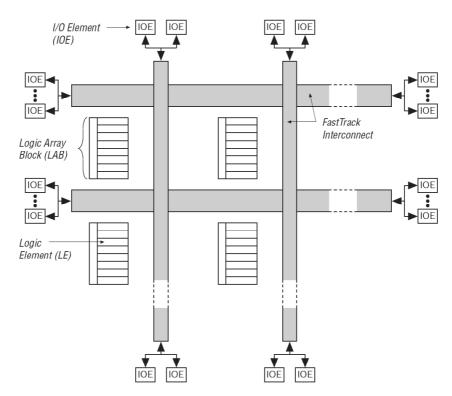

## Matthias George

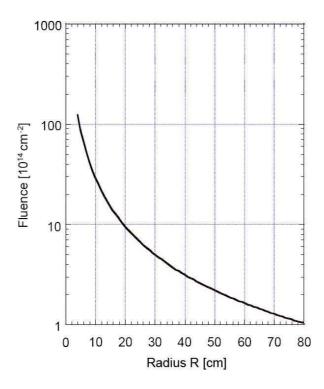

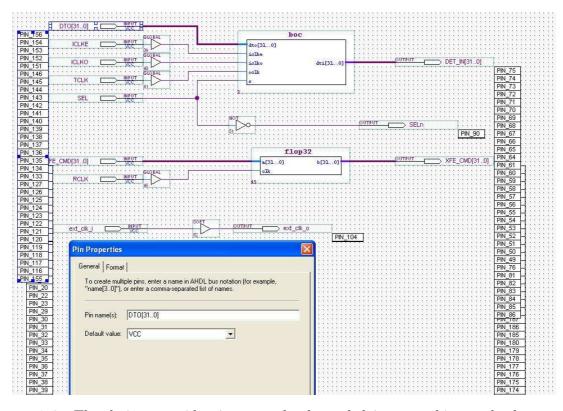

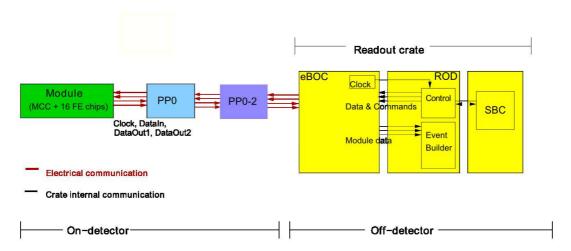

The innermost component of the ATLAS inner tracker is the pixel detector. It is made up of three barrel layers and three disk layers. The innermost barrel layer is about 5 cm away from the particle interaction point. Therefore this detector layer will be exposed to radiation more than every other detector and thus it will not be usable until the main upgrade of ATLAS after ten years of operation. A new pixel detector layer will be inserted after four years. This thesis aims to provide an electrical data read-out chain for testing of the new pixel modules.

Post address: Friedrich-Hund-Platz 1 37077 Göttingen Germany II.Physik-UniGö-Dipl-2009/03 II. Physikalisches Institut Georg-August-Universität Göttingen September 2009

# GEORG-AUGUST-UNIVERSITÄT GÖTTINGEN

# II. Physikalisches Institut

Implementation of an Electrical Read-Out System for Multi-Module Laboratory Tests of the ATLAS Pixel Detector

#### von

## Matthias George

Dieser Forschungsbericht wurde als Diplomarbeit von der Fakultät für Physik der Georg-August-Universität zu Göttingen angenommen.

Angenommen am: 01. September 2009 Referent: Prof. Dr. A. Quadt

Korreferent: PD Dr. Jörn Grosse-Knetter

# Contents

| 1.        | Intr | oduction                                                         | 1          |

|-----------|------|------------------------------------------------------------------|------------|

| 2.        | Phy  | sics                                                             | 3          |

|           | 2.1. | Introduction                                                     | 3          |

|           | 2.2. | The Standard Model                                               | 3          |

|           | 2.3. | Supersymmetry                                                    | 4          |

| 3.        |      | ATLAS Pixel Detector                                             | 7          |

|           | 3.1. | Experimental Setup - The LHC                                     | 7          |

|           | 3.2. | The ATLAS Detector                                               | 8          |

|           |      | 3.2.1. The Muon Spectrometer                                     | 9          |

|           |      | 3.2.2. The Magnet System                                         | 9          |

|           |      | 3.2.3. Calorimeters                                              | 11         |

|           |      | 3.2.4. Inner Detector                                            | 11         |

|           | 3.3. | Pixel Detector – Overview and Introduction                       | 11         |

|           | 3.4. | Pixel Modules                                                    | 13         |

|           |      | 3.4.1. Sensor                                                    | 13         |

|           |      | 3.4.2. Front End-Chip                                            | ١7         |

|           |      | 3.4.3. Bump-Bonding                                              | 20         |

|           |      | 3.4.4. Module Control Chip                                       | 21         |

|           | 3.5. | Off Detector Read-Out                                            | 24         |

|           |      | 3.5.1. Optoboard                                                 | 25         |

|           |      | 3.5.2. Back of Crate card                                        | 27         |

|           |      | 3.5.3. Read Out Driver                                           | 33         |

|           | 3.6. | ATLAS Upgrade Plans – The Insertable B-Layer                     | 36         |

| 4.        | Fiel | d Programmable Gate Arrays                                       | 89         |

|           | 4.1. | Introduction                                                     | 39         |

|           | 4.2. | 9 9                                                              | 39         |

|           |      | 4.2.1. History                                                   | 36         |

|           |      |                                                                  | <b>1</b> C |

|           |      | 4.2.3. The Altera Flex FPGA Family                               | <b>1</b> C |

|           | 4.3. | Very High Speed Integrated Circuit Hardware Description Language | 13         |

|           |      | 4.3.1. Introduction                                              | 13         |

|           |      | 4.3.2. Language Characteristics                                  | 14         |

| <b>5.</b> | Det  | ector Read Out for Multi-Module Testsystems                      | Į9         |

|           | 5.1. |                                                                  | <b>1</b> 9 |

|           | 5.2. |                                                                  | <b>1</b> 9 |

|           |      |                                                                  | 51         |

|           |      | 5.2.2 Functional Sections of the eBOC and "step 1"               | 51         |

| 5.3.   | 5.2.4.<br>Measu | Operation at 80 MBit/s – "step 2"                                        | 55<br>57       |

|--------|-----------------|--------------------------------------------------------------------------|----------------|

|        | 5.3.2.          | Trigger                                                                  | 57<br>59<br>60 |

| 6. Su  | mmary           | and Outlook                                                              | 65             |

| _      |                 | iew of FPGA behaviours on the eBOC and PP0-2 depending on the mode state | <b>67</b>      |

| Biblio | graphy          |                                                                          | 68             |

| Ackno  | wledge          | ments                                                                    | 71             |

## 1. Introduction

Scientists are on the quest for the fundamental structure of matter for many centuries. For example, Goethe expressed the question in the famous words "So that I may perceive whatever holds the world together in its innermost folds". Since those days, many huge steps in knowledge came along.

At the beginning of the 20th century, the sub-structure of atoms was discovered and protons, neutrons and electrons were considered as the smallest existing particles. Around the middle of the last century a large number of new particles have been discovered in different experiments at particle accelerators and in experimental studies concerning cosmic radiation. These new particles were arranged in symmetry groups, which lead to the conclusion that protons as well as neutrons consist of smaller particles, the quarks.

From todays view the elementary particles of our universe are quarks, leptons and bosons, which are responsible for the mediation of forces between particles. All these particles and their interactions are described very successfully by the *standard model of particle physics*. This model predicts a lot of parameters and all of them have been confirmed by several experiments. One last piece is missing to complete the standard model, the *Higgs particle*. The theory predicts that this particle emerges from self-interaction of the *Higgs field*, which is thought to be responsible for the mass-generation of all particles. The search for the *Higgs particle* is one of the main tasks of modern particle physics.

The standard model is quite successful until now, but a lot of scientists feel confident that it needs some extensions at higher energies. Some of the extension ideas are that every particle has a super-symmetric partner or the existence of additional space dimensions.

For further investigation of already known particles as well as for discovering new particles, protons or electrons or their anti-particles are accelerated to high energies and brought to collision. The recent particle accelerator is the *Large Hadron Collider*, located at the European Organization for Nuclear Research, CERN. This accelerator is designed to collide protons at a centre-of-mass energy of 14 TeV at a luminosity of  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>. Thus the LHC should open the door to an energy scale at which the *Higgs particle* can be generated and physics beyond the standard model might show up.

As important as the accelerator itself are tools to detect the generated particles. The particle detector systems provide a reconstruction of the known particles generated at the proton collisions and thus hints for unknown particles can be found. The different detector systems are typically located around the interaction point in an onion shape structure. The innermost detectors are used for particle tracking, followed by calorimeters for energy measurements and finally muon detectors for triggering and muon identification.

Since the rate of particles that have to be detected is extremely high, the detectors and the data read-out has special requirements. On the one hand they have to be very fast, on the other hand they have to be very insensitive concerning radiation damage. The highest requirements relating to these two tasks apply to the innermost detectors.

In case of the ATLAS detector the innermost part is the *pixel detector*. It is a hybrid silicon detector, composed of single modules. One of the main tasks during development of the pixel modules was to make them as radiation hard as possible combined with a low radiation length.

Although this development was very successful, a new innermost detector layer is required after half of the ATLAS lifetime, thus after about four years of operation.

The new innermost layer will be placed even closer to the interaction point than any other detector layer of ATLAS. This leads to even harder requirements concerning radiation hardness and additionally some properties of the data read-out will change. Thus a testing environment for the development of the new detector modules is needed. Since neither the existing data read-out chain nor the old testing environment can be used for testing of the new modules, a new data read-out chain is needed for this purpose.

In chapter 2, an overview on the physics that will be studied at ATLAS is given. Chapter 3 gives an overview of the ATLAS detector and a detailed overview of the ATLAS pixel detector. Additionally some details concerning the upgrade of the pixel detector are presented. An introduction to the structure and the configuration of FPGAs<sup>1</sup> is given in chapter 4. This is of special interest, since the upgrade of the existing electrical data read-out chain required main work on an FPGA. Chapter 5 describes the electrical read-out chain in detail as well as the changes that have been done to upgrade the system for the new pixel modules.

<sup>&</sup>lt;sup>1</sup>Field Programmable Gate Arrays

# 2. Physics

#### 2.1. Introduction

This chapter summarizes the standard model of particle physics. Subsequently, supersymmetry is introduced as one possible extension to the standard model. The search for the latter is one of the many motivations to build the LHC.

#### 2.2. The Standard Model

The standard model of particle physics [1] describes the properties and interactions of elementary particles very precisely on small distances, where gravitational effects can be ignored. The predictions of the standard model have been confirmed with an extremely high accuracy in precision measurements.

The standard model has been developed in the early 1970s. It is a quantum field theory, where the Lagrangian is invariant under  $SU(3)_C \times SU(2)_L \times U(1)_Y$  gauge transformations and consistent with quantum mechanics as well as special relativity.

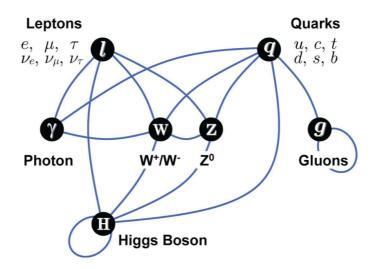

In this model the elementary particles are divided into three groups. The leptons, the quarks (both spin- $\frac{1}{2}$  particles) and the spin-1 and spin-0 gauge bosons. The quarks and leptons are ordered in three families. They are listed in table 2.1. The electroweak and the strong interactions act via gauge bosons that are exchanged between the particles. An overview of these bosons is given in figure 2.1.

| Family 1 |                                                   | Family 2   |                                                   | Family 3   |                                                   |                          |

|----------|---------------------------------------------------|------------|---------------------------------------------------|------------|---------------------------------------------------|--------------------------|

| symbol   | $\max \left[\frac{\text{MeV}}{\text{c}^2}\right]$ | symbol     | $\max \left[\frac{\text{GeV}}{\text{c}^2}\right]$ | symbol     | $\max \left[\frac{\text{GeV}}{\text{c}^2}\right]$ | charge [e <sup>-</sup> ] |

|          | leptons                                           |            |                                                   |            |                                                   |                          |

| $ u_e$   | $< 3 \times 10^{-6}$                              | $ u_{\mu}$ | $< 0.19 \times 10^{-3}$                           | $ u_{	au}$ | 0.0182                                            | 0                        |

| e        | 0.511                                             | $\mu$      | 0.1057                                            | au         | 1.777                                             | -1                       |

|          | quarks                                            |            |                                                   |            |                                                   |                          |

| u        | 1.5 - 3                                           | С          | $1.25 \pm 0.09$                                   | t          | $174.2 \pm 3.3$                                   | $+\frac{2}{3}$           |

| d        | 3 - 7                                             | s          | $0.095 \pm 0.025$                                 | b          | 4.2 - 4.7                                         | $-\frac{1}{3}$           |

Table 2.1.: The most important properties of the three lepton and quark generations.

Figure 2.1.: Overview of the different bosons and their interactions between the particles of the standard model.

The standard model without extension leads to a problem. The requirement of local gauge invariance implies, that the gauge bosons are massless. However, it was found experimentally that the  $W^{\pm}$  and the Z are massive. Peter Higgs [2] predicted in 1964 a scalar background field that would solve this problem via spontaneous symmetry breaking. Through self-interaction of this field a new particle would be generated, the *Higgs particle*. All of its parameters are predicted by the model, except the mass. The *Higgs particle* has not been found yet. Only a lower limit on its mass 114.4 GeV [3] has been set and an upper limit follows from theoretical considerations at around 1 TeV. The LHC design allows Higgs-searches over the whole possible mass-range.

Altogether the model contains some properties and questions that motivate a search beyond the standard model. For example:

- What are the 19 free parameters?

- Is the *Higgs boson* of standard model type?

- Does a unification of the fundamental forces exist?

- Astro-particle physics delivered a remarkable number of observations that can not be explained by the standard model, e.g. why does an asymmetry between particles and anti-particles in the universe exist?

- What is dark matter?

- How can the hierarchy problem be solved?

## 2.3. Supersymmetry

Since the standard model leaves some important and interesting questions unanswered, new theories are being developed and summarized as "Physics beyond the Standard Model". One of the most promising models is supersymmetry. With the help of this theory several problems would be solved. Firstly it would provide an answer to the hierarchy problem. Secondly a

unification of the electro-magnetic force, the weak force and the strong force would be achieved at high energy scales. And thirdly the string theory seems to require supersymmetry for its consistency, whereas the string theory could be essential to add gravity to the existing models. For details see [4].

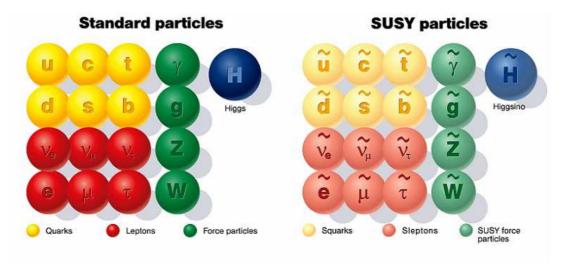

Supersymmetry predicts that every elementary particle has a superpartner. These superpartners have the same mass, coupling and quantum numbers as the standard model particles. Only their spin differs by  $\frac{1}{2}$ . Since the charges of the standard model fermions and bosons differ, it is not possible that some of these particles are superpartners. Thus superpartner particles for all standard model particles must exist in the supersymmetric model, whereas until now none of the superpartners have been discovered. This means that supersymmetry must somehow be broken. An overview of the supersymmetric particle zoo is given in figure 2.2.

Figure 2.2.: On the left side, the known particle zoo of the standard model plus the Higgs particle is shown, the right side shows the particles resulting of an extension by supersymmetry.

One of the most promising theories to be discovered at LHC is a minimal supersymmetric extension of the standard model. This theory is called *Minimal Supersymmetric Standard Model* (MSSM) and was originally invented in 1981 to solve the hierarchy problem. In case hints for the MSSM-theory are found at LHC, it could provide a good candidate for cold dark matter particles.

In summary this was only a short overview of some research areas that are investigated by the LHC experiments. Since the number of open questions that could be answered or what new hints could be found by the LHC experiments is huge and their scale reaches from sub-atomic order to the scale of galaxies, scientists all over the world are looking forward to the launch of this experiment.

# 3. The ATLAS Pixel Detector

## 3.1. Experimental Setup - The LHC

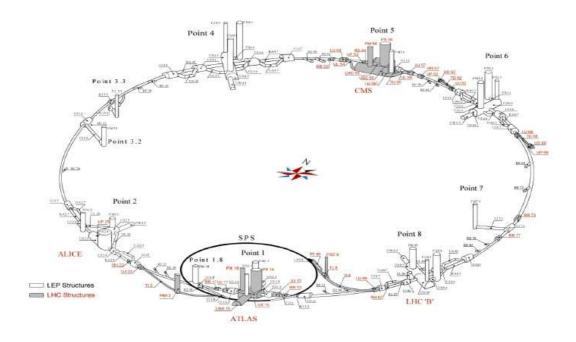

The Large Hadron Collider<sup>1</sup> (short: LHC) is the biggest machine humans ever built. It is a circular hadron accelerator, located at CERN<sup>2</sup>, Geneva. In total it has a circumference of about 27 km, set up in a tunnel 100 m below surface, that was previously used by the Large Electron Positron Collider experiment (see figure 3.1). In the LHC, protons are accelerated using several pre-accelerators and finally the LHC itself so that collisions take place with a center of mass energy of up to 14 TeV. Thus the LHC outranges all other accelerator experiments by approximately one order of magnitude.

Figure 3.1.: Overview on the LHC and positions of the experiments [5].

The run schedule foresees to have 2808 proton packages in the LHC ring, each consisting of  $1.1 \times 10^{11}$  particles. The distance between two packages will be 25 ns and luminosity is planned to be ramped up to  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>. There are four points at which collisions are planned to take place with a rate of 40 MHz. At each collision on average about 20 inelastic interactions are expected, whereas the mean number of produced charged particles is expected to be around 1000. At every collision point an experiment is placed, of which two cover the whole spectrum

<sup>&</sup>lt;sup>1</sup>www.cern.ch/lhc

<sup>&</sup>lt;sup>2</sup>Conseil Européen pour la Recherche Nucléaire

of physics questions handled at the LHC: ATLAS<sup>3</sup> [6] and CMS<sup>4</sup> [7]. The other two experiments are designed for special questions. On the one hand there is LHC-B [8], concentrating on b-physics and on the other hand ALICE<sup>5</sup>. ALICE is designed to investigate lead-lead collisions that take place alternatively to the proton-proton collisions. For the proton runs the design values of LHC are shown in table 3.1.

| circumference             | 26659 m                                 |

|---------------------------|-----------------------------------------|

| magnetic field strength   | 8.4 T                                   |

| centre of mass energy     | 14 TeV                                  |

| number of proton packages | 2808                                    |

| protons per package       | $1.1 \times 10^{11}$                    |

| distance of packages      | 25  ns                                  |

| collision rate            | 40 MHz                                  |

| luminosity                | $10^{34} \text{ cm}^{-2} \text{s}^{-1}$ |

Table 3.1.: LHC design values for proton runs [5].

### 3.2. The ATLAS Detector

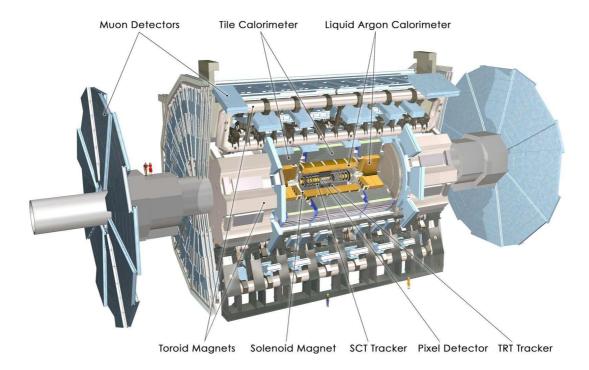

To get an overview of the layout, figure 3.2 shows the setup of ATLAS.

Figure 3.2.: Layout of the ATLAS Detector and positions of the sub-detectors [6].

The detector has been built in an onion shape structure [9]. This means, that ATLAS consists

<sup>&</sup>lt;sup>3</sup>A Toroidal LHC Apparatus

<sup>&</sup>lt;sup>4</sup>Compact Muon Solenoid

<sup>&</sup>lt;sup>5</sup>A LHC Ion Collider Experiment

of several subdetectors, whereas each is designed for special purposes, e.g. precise tracking or energy measurement. All these detectors are nested together in a way such that (almost) every direction in space is covered.

In the ATLAS layout overview one can see that the outermost parts of the whole experiment are the muon chambers. For detection of the muon's momentum this subdetector is placed in a  $0.5~\rm T$  toroidal magnetic field. Moreover the muon chambers are used for triggering. The toroidal magnets are one of the most characteristical attributes in the shape of ATLAS. The next internal subdetectors are the hadronic and the electromagnetic calorimeter, which measure the energy of particles and jets. Finally there is the "Inner Detector", consisting of a transition radiation tracker, a silicon strip detector and a silicon pixel detector. The Inner Detector is used for precise tracking of charged particles. It is covered by a  $2~\rm T$  solenoid magnetic field to provide a momentum measurement of the particles. All these different subdetectors and magnets together lead to a size of about  $25~\rm m \times 44~m$  and a mass of around 7000 tons.

For the detector design several aspects had to be taken into account. In summary the highest priority aims were: Firstly a  $4\pi$  coverage of the interaction point had to be realized. Especially by the calorimeters, which in particular is important for measurement of missing transverse energy caused by unknown particles. But of course for whole ATLAS a coverage in  $\Phi$ -direction and almost full coverage in  $\eta^6$  were aimed to cover events – as far as possible – completely. Secondly a precise measurement of muon momentum was desired. Thirdly an efficient and extremely precise particle tracking at high luminosities as well as at low luminosities was required to provide full event reconstruction.

#### 3.2.1. The Muon Spectrometer

The muon system uses different detectors for triggering and tracking. For triggering Resistive Plate Chambers (RPCs), which are operated in avalanche mode, are used in the barrel region and Thin Gap Chambers (TGCs), operated in saturated mode, are used in the end-caps. For high resolution tracking on the one hand Monitored Drift Tubes (MDTs) are used for  $|\eta| < 2$ . The MDTs are drift chambers made of aluminium and filled with a gas mixture that survives high doses of radiation without ageing. On the other hand, Cathode Strip Chambers (CSCs), which are multi-wire proportional chambers, are applied for  $2 < |\eta| < 2.7$ . The first two detector types are mainly used for event triggering since they are faster – in the order of 2 ns respectively 4 ns – than MDTs and CSCs. However they are not as precise in terms of spatial resolution as the latter ones. MDTs and CSCs have a spatial resolution in the order of 50  $\mu m$  but are too slow for trigger tasks.

#### 3.2.2. The Magnet System

The magnetic field that was requested by the different ATLAS subdetector groups is realized using four superconducting magnets [10]. The Central Solenoid, the Barrel Toroid and two End-Cap Toroids.

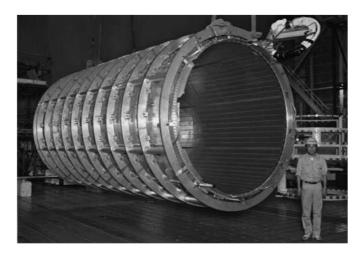

The Central Solenoid (CS) provides an axial magnetic field with a peak field strength of about 2.6 T for the central detector. This requires a current of 7600 A for the 5.3 m  $\times$  2.4 m big magnet. It is integrated into the liquid Argon calorimeter cryostat and has been tested up to 8400 A in the factory and up to 8100 A after assembly at the detector site. Figure 3.3 illustrates the dimensions of the Central Solenoid.

<sup>&</sup>lt;sup>6</sup>pseudorapidity  $\eta$  is defined as  $\eta = \ln \tan \frac{\theta}{2}$ , where  $\theta$  is the polar angle of the particle relative to the beam line

Figure 3.3.: ATLAS Central Solenoid ready for transport to CERN. On the outside supporting rings to keep the magnets' shape are visible [10].

The two End-Cap Toroids (ECT) consist of 5 m  $\times$  5 m coil modules. The coil modules are linked by eight so called keystone boxes. The ECT is pulled inside the Barrel Toroid with up to 300 tons, because the magnetic windings of the toroids overlap. The peak field provided is about 4.1 T.

Finally the Barrel Toroid (BT) is made up of eight racetrack coils, each with a size of 5 m  $\times$  25 m. An inner and outer set of huge rings keeps the coils in their toroidal shape. The coils have been tested up to a current of 22 kA. The peak field provided by the barrel toroid coils is about 3.9 T. All in all the toroid is assembled on 18 feet on the ground.

Figure 3.4 gives an overview of the toroid magnet system.

Figure 3.4.: Schematic overview of the Barrel Toroid, consisting of eight coils, and the End-Cap Toroids, where one is inserted and one retracted [10].

#### 3.2.3. Calorimeters

The calorimeter system is subdivided into the hadronic and the electromagnetic calorimeter. The hadronic calorimeter is a sampling calorimeter which in the barrel part is made of iron absorbers and plastic scintillators. In the regions of higher pseudorapidity copper or tungsten and liquid argon are used because of the higher radiation dose in this area. The electromagnetic calorimeter is also a sampling calorimeter, made out of lead absorbers in liquid argon. Both calorimeters are designed such that they have a thickness in the order of 20 interaction lengths to ensure absorption of the particle species they are designed for. Using the shower depth and the cone size of the emerging particle shower, the particles' energy can be calculated precisely.

#### 3.2.4. Inner Detector

Compared to the size of ATLAS the Inner Detector is quite small with dimensions of 2.3 m  $\times$  7 m, although this volume houses three different detector types. One of them is the Transition Radiation Tracker (TRT). The TRT consists of a central barrel and two end caps on both sides [11]. Altogether it provides 420,000 read-out channels and is used for tracking of charged particles as well as electron identification. The detector is made up of straws, filled with a gas mixture and one sense wire per straw. On average a particle crosses 36 straws for  $|\eta| < 2.1$ . Every time the particle traverses a transition, photons are emitted. This transition radiation is used to distinguish between electrons and heavy particles, e.g. pions. On top of that the gas mixture in the straws is ionized, which causes the main tracking signal that is detected. This delivers a resolution of about 130  $\mu m$ .

On the way from the outer detector types to the interaction point the next sub-detector is the Semi Conductor Tracker (SCT). The SCT is assembled in four barrel layers and nine disks at each of the two end-caps. The barrels and disks are composed of modules at which two pairs of single sided p-in-n microstrip sensors are glued back to back. The silicon sensors are rotated at a 40 mrad stereo angle, which guarantees two-dimensional hit information. As opposed to the disk modules, the barrel modules are all identical. Depending on their position the disk modules have four different geometries. All in all the SCT provides 6.2 million read-out channels and a spatial resolution of 16  $\mu$ m in  $R\Phi$ -direction and 580  $\mu$ m in z-direction.

Because the pixel detector – and especially its communication with the outside world – is the main topic of this thesis, it is described in detail in the next section.

#### 3.3. Pixel Detector – Overview and Introduction

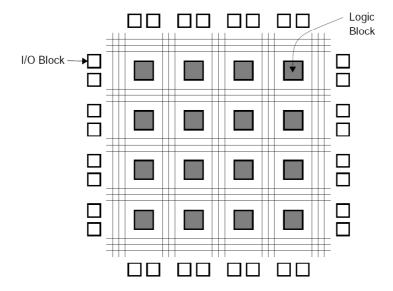

The pixel detector is the innermost part of the ATLAS detector. It is placed close to the beam line, which leads to special requirements concerning spatial resolution, radiation hardness, two particle separation and occupancy tolerance. By using a pixel size of 50  $\mu$ m × 400  $\mu$ m the single channel occupancy is kept low enough to ensure an efficient read-out. The concept of pixel detectors is to deliver truly two-dimensional track measurements. Compared to other detector systems, where the two-dimensionality is based on added one-dimensional track information, there is not the risk of getting "ghost hits" in case of multiple hits per detector unit. Since the pixel detector has an excellent single-point resolution and provides the previously mentioned features, it gives the feasibility of b-tagging, which is crucial for the detection of SUSY and Higgs signatures.

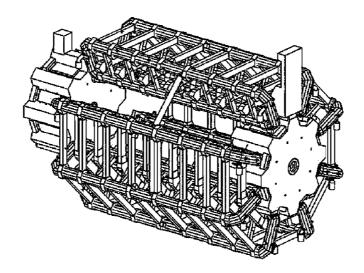

The detector is arranged in three barrel layers in the centre part and three disk layers in both forward directions, as can be seen in figure 3.5. This set-up delivers three space points per

Figure 3.5.: Schematic view of the ATLAS Pixel Detector.

charged particle for a pseudorapidity of up to  $|\eta| = 2.5$ . All barrel layers are composed of several staves, where the number of staves is different for every layer, since they all have different radii (see table 3.2). The staves themselves are all mechanically the same. They are arranged in a way, that there is a slight overlap in z-direction to ensure a full coverage in this direction. Every stave consists of 13 active parts, the *pixel modules* (see next section).

In contrast the disk layers are all set up the same way. They are subdivided into eight sectors, where every sector has three modules on the front side and three modules on the backside. Again the modules on front- and backside overlap to avoid gaps in the active area. An overview of the different configurations of the layers is given in table 3.2 - for barrel layers and disk layers outwards seen from the interaction point.

|         | Radius (mm)     | No. of Staves | No. of Modules |

|---------|-----------------|---------------|----------------|

| B-Layer | 50.5            | 22            | 286            |

| Layer 1 | 88.5            | 38            | 494            |

| Layer 2 | 122.5           | 52            | 676            |

|         | z-Position (mm) | Sectors       | Modules        |

| Disk 1  | $\pm 495$       | 8+8           | 48+48          |

| Disk 2  | $\pm 580$       | 8+8           | 48 + 48        |

| Disk 3  | $\pm 650$       | 8+8           | 48+48          |

| Total   |                 |               | 1744           |

Table 3.2.: Set-up and dimensions of the ATLAS Pixel Detector [12].

#### 3.4. Pixel Modules

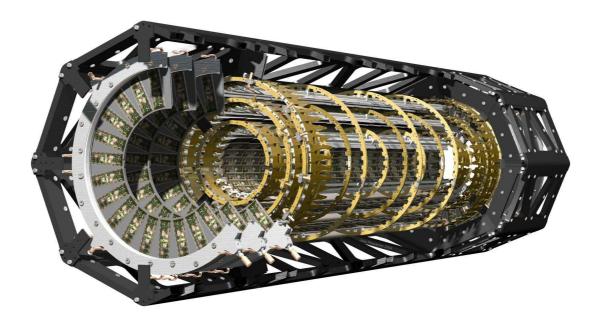

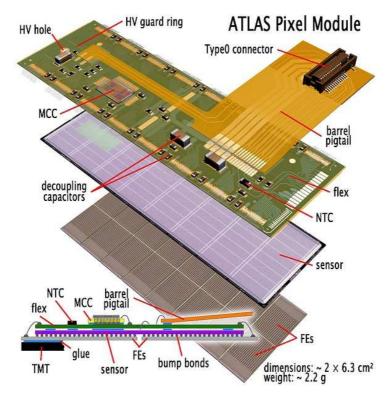

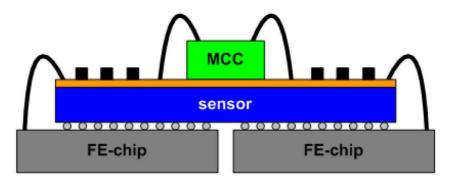

The pixel detectors' smallest active unit is called "pixel module". A pixel module consists of a  $2 \times 6$  cm<sup>2</sup> silicon sensor, the read-out electronics and a kapton-flex PCB<sup>7</sup>, see figure 3.6.

Figure 3.6.: Schematic view of the pixel module components.

Each sensor is subdivided into 47,232 pixels, with a size of 50  $\mu$ m × 400  $\mu$ m or – due to geometrical reasons – 50  $\mu$ m × 600  $\mu$ m. Every pixel is connected to a single electronic cell via bump bonds (see subsection 3.4.3). The read-out electronics is arranged in 16 ASICs<sup>8</sup>, the Front-End chips (short: FE-chips). Arriving signals are amplified and digitized by the FE-chips and forwarded to the MCC<sup>9</sup>. The major task of the MCC is communication with the off-detector read-out electronics (section 3.5). For the connection between FE-chips and MCC, the wire-bond technology was chosen. A more detailed view on the just mentioned parts follows in the next sections. Furthermore, every pixel module is equipped with a Negative Temperature Coefficient Thermistor (NTC) for temperature monitoring of every module.

#### **3.4.1.** Sensor

#### **Basic Principles of Semiconductor Detectors**

The chosen semiconductor sensor material for the ATLAS Pixel Detector is diffusion-oxygenated float zone silicon. In case a charged particle traverses a semiconductor, electron-hole pairs are generated along its path due to the particles' energy loss in the material. For silicon, the energy gap in the band structure, which is the energy needed to ionize an atom of the particular

<sup>&</sup>lt;sup>7</sup>Printed Circuit Board

<sup>&</sup>lt;sup>8</sup>Application Specific Integrated Circuits

<sup>&</sup>lt;sup>9</sup>Module Control Chip, see subsection 3.4.4

material, is 1.12 eV. However the mean energy that is needed to produce an electron-hole pair is 3.62 eV. The difference can be explained by phonons, or rather thermal energy at the end, produced during this process.

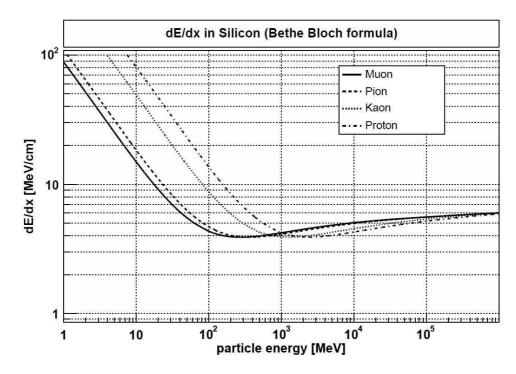

This energy loss as a function of track length is described by the Bethe-Bloch formula for particles with  $m \gg m_e$ .

$$-\frac{dE}{dx} = 2\pi N_a r_e^2 m_e c^2 \rho \frac{Z}{A} \frac{z^2}{\beta^2} \cdot \left[ \ln \left( \frac{2m_e \gamma^2 v^2 W_{max}}{I^2} - 2\beta^2 - \delta - 2\frac{C}{Z} \right) \right]$$

(3.1)

with (in case of silicon):

$\frac{dE}{dx}$ : mean energy loss per track length

$N_a$ : Avogadro's number:  $6.022 \times 10^{23} \text{ mol}^{-1}$

$r_e$ : classical electron radius:  $2.817 \times 10^{-13}$  cm

$m_e$ : electron mass: 511 keV

$\rho$ : density of absorbing material: 2.33  $\frac{g}{cm^3}$

I: average effective ionization potential:  $\approx 173 \text{ eV}$

Z: atomic number of absorbing material: 14

A: atomic weight of absorbing material: 28

z: charge of traversing particle in units of e

$\beta$ :  $\frac{v}{c}$  speed of traversing particle in terms of c

$\gamma$ :  $\frac{1}{\sqrt{1-\beta^2}}$

$\delta$ : density correction

C: shell correction

$W_{max}$ :  $2m_ec^2\beta^2\gamma^2$  if  $M\gg m_e$  maximum energy transfer in a single head on head collision

In formula 3.1 the density effect correction  $\delta$  – which is especially important for higher energies – and the shell correction C – important for low energies – are included. The formula is valid for  $\beta$ -values down to  $\beta \approx 0.1$ .

The polarization process is caused by the presence of the electric field which involves a polarization of the atoms along the path of the traversing particle. Hence there is a shielding from the full electric field for electrons that are far away from this path. Therefore the density effect depends on the density of the absorbing material.

The wrong assumption of a stationary electron in the material is the reason for the integrated shell correction, which reduces the energy loss at low energies.

The Bethe-Bloch formula has a minimum at around  $v \approx 0.96\,$  c which means  $\beta\gamma\approx 3.5.$  Particles with an energy corresponding to that point are called minimum ionizing particles, or short m.i.p. For the example of 250  $\mu$ m thick silicon figure 3.7 shows that a minimum ionizing pion with a mass of  $m_{pion}=139.57\,$ MeV has an energy loss of about 97.5 keV, which corresponds to a generation of around 27,000 electron-hole pairs. The most probable value for the energy loss is  $\approx 69.9\,$ keV which corresponds to a generation of about 19,300 electron-hole pairs. The difference can be explained by the asymmetry of the energy loss density function. It is not a Gaussian, but has – due to possible interactions with higher energy transfer – a tail to higher energies.

#### The ATLAS Pixel sensor

The silicon sensor of the ATLAS Pixel Detector [14] has dimensions of  $63 \times 18.6 \times 0.25 \text{ mm}^3$  with an active area of  $60.8 \times 16.4 \text{ mm}^2$ . As the name suggests the sensor is subdivided into

Figure 3.7.: Correlation between different particles' energies and their energy loss in 250  $\mu m$  thick silicon [13].

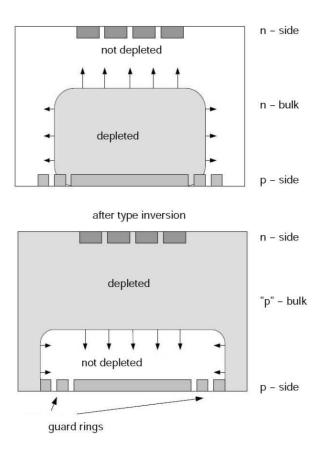

pixels to yield true 2-dimensional spatial information for every hit. The chosen sensor type is  $n^+$  in n which on the one hand makes a preparation of both sensor sides necessary, but offers on the other hand a lot of advantages. Irradiation of the sensor causes a type inversion of the n-bulk, see figure 3.8. With a change of the concentration of the effective doping for increasing irradiation a type inversion of the n-bulk into a "p"-bulk occurs. The change of the effective doping concentration entails a change of the depletion voltage that is needed for detector operation. The depletion of the sensor is essential for tracking, because without depletion the - in case of a particle crossing - emerging electron-hole pairs would immediately recombine. Thus the signal would be lost. In the initial state the depletion zone grows from the sensor's back side, whereas it grows from the pixel side after type inversion. This offers an isolation of the pixels against each other, additionally to the used p-spray technique, even for a not completely depleted sensor. In the initial (unirradiated) state the depletion voltage is in the order of  $|V_{depl}| = 70$  V and a bias voltage of  $|V_{bias}| = 150$  V and can be pushed up to  $|V_{depl}| = 700$  V with increasing irradiation. Because the sensor's edges are electrically conductive, guard rings are used to avoid the destruction of the sensor.

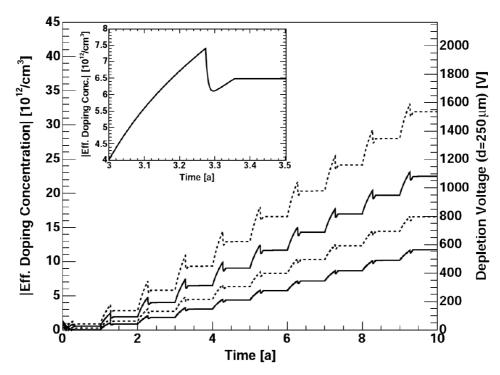

Since the Pixel Detector is placed extremely close to the interaction point the development of the used silicon came along with many hard requirements. After a long time of research the idea of oxygen-doped silicon arose and turned out as the best solution in terms of radiation hardness [15]. The reason for this choice is shown in figure 3.9. It shows a comparison of the needed depletion voltages for standard silicon and for oxygenated silicon based on the original LHC runschedule for the first 10 years. The depletion voltage increases with time because the continuous irradiation changes the doping concentration and thus the ohmic resistance. Several tests showed that the dimension of the just mentioned sensor-effects is quite temperature sensitive. It turned out that the optimal operating temperature for the sensor is  $-10^{\circ}$ C. At higher temperatures – during breaks – the silicon can partially repair itself, which is called annealing. This effect

Figure 3.8.: Development of the depleted region before and after type-inversion [12].

explains the drops of the needed depletion voltage in figure 3.9 once a year. However this positive effect turns into the opposite if the sensor is kept for a long time at a higher temperature. Because of this the sensors are warmed up for 20 days per year and afterwards cooled down to operating temperature again. The plot shows, that Layer 1, and thus Layer 2 as well, can be operated fully depleted for the whole run-time due to the temperature cycling and oxygen doping techniques. For the B-Layer, the limit is expected after about 7 years. After this time the needed depletion voltage for the sensor is expected to be above the limit of  $|V_{depl}| = 700 \text{ V}$ . Thus the electrons and holes can not be separated by the electric field anymore and the signal is lost. That is why a new B-Layer will be inserted after about 5 years (see subsection 3.6).

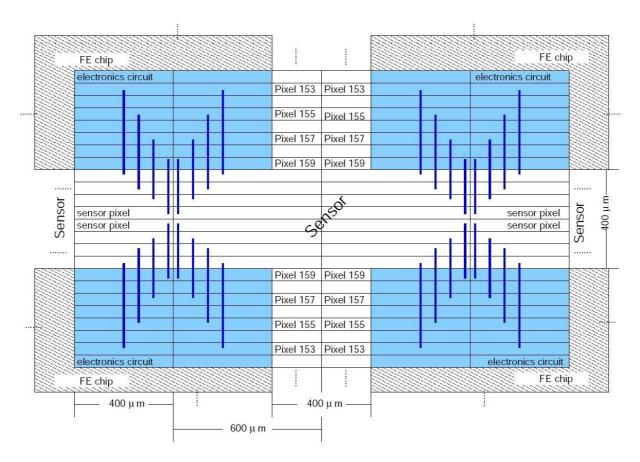

Most of the sensor pixels, as already mentioned, have a size of  $50~\mu\text{m} \times 400~\mu\text{m}$  which results in a spatial resolution of  $15~\mu\text{m}$  in  $R\Phi$ -direction and  $115~\mu\text{m}$  in z-direction. Because every single sensor pixel is connected to an electronics circuit, the pixels had to be arranged in a way that somehow fits with the design of the 16 Front End-chips per sensor. The circuits on the FE-chips are arranged in 160 rows and 18 columns. Per sensor eight (long side) times two (short side) FE-chips are used. In case of pixels with all the same size, this would result in dead regions at every gap between two FE-chips. This problem has been solved by an extended pixel size of  $50~\mu\text{m} \times 600~\mu\text{m}$  at the long sides of the chips, called long pixels. On the short side of each chip eight pixels are not covered. Every uncovered pixel is ganged to a connected pixel. These pixels are called ganged pixels, since they are connected with another pixel to one electronics cell. This results in four electronic cells per column that are each connected to two pixel cells, thus four ganged pixels per column. As an overview figure 3.10 shows the sensor's top metallisation. It also shows that the four ganged pixels are located in the outer area of the sensor. Thereby

Figure 3.9.: Depletion Voltages for pure silicon (dashed lines) and oxygenated silicon (solid lines) for 10 years of operation. The upper two lines are for the B-Layer, the lower two lines are for Layer 1 [16].

every second pixel of the outer eight pixels is connected to one pixel of the following block of four adjacent pixels. Thus a distinction which of the two ganged pixels was hit is possible, because at least two neighbouring cells show a signal in case of a hit. By investigation of the hit pattern it can be calculated which of the two ganged cells has been traversed by the particle. Altogether the picture in figure 3.10 shows the normal pixels (50  $\mu$ m × 400  $\mu$ m in size), long pixels (50  $\mu$ m × 600  $\mu$ m), ganged pixels and long ganged pixels. The different types are clearly visible e.g. in threshold-scans (see chapter 5) where different pixel types show a different noise behaviour.

#### 3.4.2. Front End-Chip

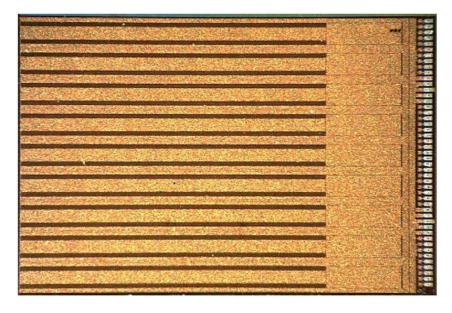

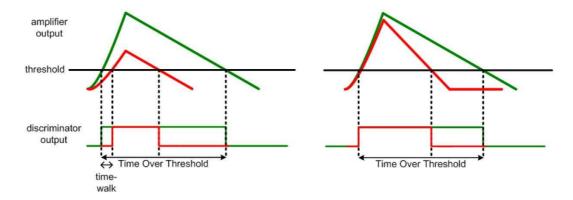

Sixteen Front End-chips per pixel module are needed to digitize the signals of one sensor. The chips have been designed in a radiation hard deep sub micron technology and were produced in a 250 nm process at IBM [17]. Every FE-chip is organized into 9 column pairs and 160 rows (see figure 3.11), which means 2880 read-out cells per chip, each with a size of 400  $\mu$ m × 50  $\mu$ m. This results in a chip-size of 7.2 mm × 10.8 mm. The chip design contains a digital part and an analogue part, each of them has its own design supply voltage. For the digital part, this is  $V_{DD} = 2.0 \text{ V}$  and for the analogue part  $V_{DDA} = 1.6 \text{ V}$ .

Every read-out cell contains two cascaded amplifiers, which are followed by a very fast differential discriminator. The discriminator supports adjustable threshold values from 0  $e^-$  up to 12,000  $e^-$  [18]. The benchmark is 4000  $e^-$ , which permits efficient tracking, especially compared to the expected charge for a m.i.p. of around 19,300  $e^-$  at the beginning and still about 10,000  $e^-$  at the end of the irradiation time. These numbers will fluctuate on a small scale for the individual pixels due to noise in the order of 200  $e^-$ . The adjustment can be done during

Figure 3.10.: Schematic view of the sensor showing the region where four FE-chips meet. Pixel cells are painted as horizontal cuboids, whereas ganged pixels have junctions drawn as vertical lines [12].

Figure 3.11.: Photomicrograph of a FE-chip, showing the alignment of the column pairs [17].

operation and is realized using two DACs<sup>10</sup>. The threshold of the whole chip can be changed using a coarse 5-bit global DAC (short: GDAC). On top of that, every cell can be fine-tuned individually using a 7-bit trim DAC (short: TDAC). This tuning capability is quite important, since a homogeneous answer of the electronics is needed for a fixed injected charge to provide a reliable tracking.

The analogue part of the chip has two amplifier stages, where the first stage is a charge sensitive (pre-)amplifier. It is equipped with a 10 fF feedback capacitor for charge collection, which is discharged by a constant current source. The discharge current can be adjusted using two different DACs. On the one hand there is the global 8-bit IF-DAC and on the other hand the individually settable 3-bit feedback DAC. These DACs are used to achieve a homogeneous amplifier recovery time over the chips.

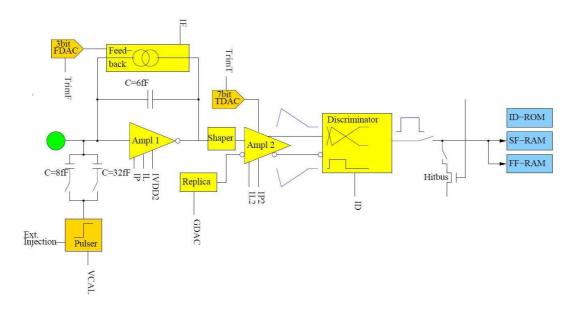

To test the behaviour of these parts a charge injection circuit has been implemented (see chapter 5.3). A schematic view of the analogue part is given in figure 3.12. In case of a charge

Figure 3.12.: Pixel unit cell in a schematic drawing [12].

injection into the electronics circuit the amplified signal rises and after a short time it exceeds the threshold. At this point a time stamp is set (leading edge time, short: LE). The falling edge of the signal is linear, so that altogether the signal shape is almost triangular. Together with the leading edge time and the also recorded time when the signal drops below the threshold again, the charge deposited in the sensor can be calculated. The time difference between these two events is called time-over-threshold (short: ToT). Thus the energy loss of a particle that traversed the sensor can be measured with the FE-chips, using the recorded 8-bit ToT information [19]. The relation between the amplifier output and the ToT-value is visualized in figure 3.13. One of the pre-amplifier's characteristics is that its output signal always peaks at the same time, for high charges as well as for low charges. This leads to the so called timewalk-effect, which is also visible in figure 3.13. For a smaller charge the rising edge of the amplifier is not as steep as for a high charge. Thus the threshold is crossed later and – since a typical signal is about 30 bunch-crossings long – this may cause a signal delay higher than a 40 MHz clock cycle. In order not to assign a hit to the wrong bunch-crossing, the FE-chip has a mechanism implemented to recover

<sup>&</sup>lt;sup>10</sup>Digital Analogue Converters

Figure 3.13.: Amplifier and discriminator outputs for a high charge (green) and a low charge (red) and the resulting ToT-values. On the left side the timewalk-effect is shown, on the right side the different outcomes in case of strongly differing discharge currents for almost the same charge [19].

hits that are recorded too late because of the timewalk. This mechanism uses the also recorded time-stamp of each hit and thus hits can later be reassigned to the correct bunch-crossing. Hits with a too small ToT-value can directly be deleted, since they have a large probability to be a noise hit.

For every detected rising edge the Gray coded<sup>11</sup> time stamp of the leading edge is stored in the 8-bit LE-RAM, which is a piece of the FE's digital part. There are two more RAMs per cell. On the one hand there is another 8-bit RAM to store the pixel address and on the other hand an 8-bit RAM to store the time stamp of the falling edge in case of a hit detected (FE-RAM).

In this case, a hit flag is set for the related pixel, which causes the read-out logic to check all the pixels of the column pair. In case multiple pixels are hit, first the topmost one is read out. The pixel address, leading edge (LE) time stamp and falling edge (FE) time stamp are sent to the end-of-column logic, where the ToT value is calculated and afterwards all the hit information is stored in one of the 64 available buffer cells. Then the hit flag for this pixel has to be reset and the next pixel in the chain is read out. For the time that is needed to read out the chain a freeze signal is sent, which prevents pixels from setting their hit flags. In case of new hits during the freeze signal is active, the information is stored in the pixels until the readout is released again.

The next step for hits stored in the end-of-column buffers is that their LE-time stamps are compared to a readout time stamp counter. For hits with fitting time stamps and a Level1 trigger signal the data-travelling continues to the serializer. From there they are forwarded to the MCC (see chapter 3.4.4) together with the internally calculated bunch-crossing ID. This is needed to assign every hit to its event and hence for event-building in the MCC. All hits that passed the previous requirements apart from having an active Level1 signal are deleted.

#### 3.4.3. Bump-Bonding

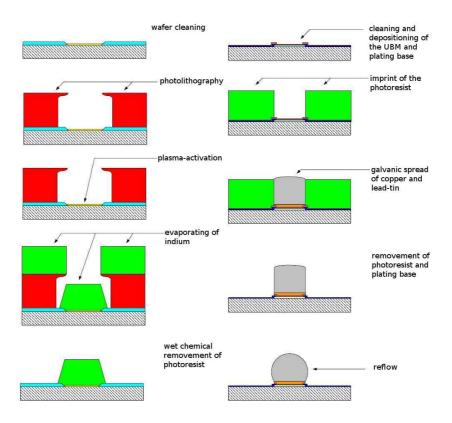

As shown in figure 3.14 the pixel sensor and the FE-chips are connected using a special technique. They are connected via small bumps, made out of either indium or lead-tin [20]. The production of the bumps has been realized in four steps.

<sup>&</sup>lt;sup>11</sup>Gray code is a binary numeral system where two successive values differ in only one bit, which results in a lower digital chip activity

- 1. For the modules connected with indium bumps, the sensor wafers as well as the FE-chip wafers were equipped with bumps. In contrast the lead-tin connected modules only got bumps on the FE-chip wafers and a special "Under Bump Metallization" on the sensor wafers.

- 2. The FE-wafers are thinned down to 210  $\mu$ m.

- 3. Both wafer types are cut and after a quality check only the sensors and FE-chips marked as good are chosen for further processing.

- 4. Using the flip-chip technique, the FE-chips are put and aligned on the sensors and afterwards connected with a defined pressure and temperature.

After assembly the indium bumps have a cylindrical shape with a radius of about 20  $\mu$ m and a height of around 8  $\mu$ m. The lead-tin bumps have a spherical shape with about 20  $\mu$ m diameter. Another difference between the two materials is that lead-tin bumps have a resistance lower than 1  $\Omega$ , whilst indium bumps have a resistance of several ten Ohms [21]. In figure 3.15, the important steps in the production of both bump-types are shown.

Figure 3.14.: Schematic side-view of a pixel module [19].

#### 3.4.4. Module Control Chip

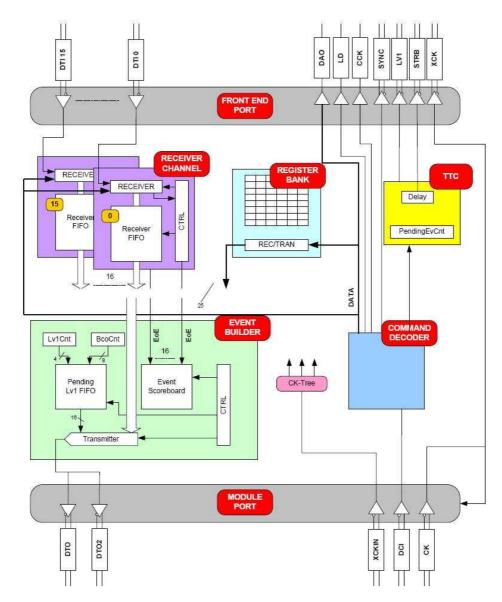

Each pixel module is featured with a Module Control Chip (MCC) which has bidirectional tasks [22]. On the one hand it receives configuration data, triggers and the clock signal and has to distribute these signals to all 16 FE-chips on the module. On the other hand it is responsible for data read-out and event fragment building. All data that has to be passed to the FE-chips is received by the on-detector (opto)-electrical interface and accordingly the read out event data is sent to the off-detector electronics by this interface, see sections 3.5.1 and 5.2.1.

The received clock signal is transformed by the MCC into the 40 MHz clock that is needed for the module read-out (XCK) and into the 5 MHz clock used for module configuration (CCK)<sup>12</sup>. Furthermore, the received configuration data has to be transformed into another data format before it can be transmitted to the FE-chips. For testing purposes the configuration data can be read out from the FE-chips.

For received timing and reset signals the MCC's task is not only to distribute them to all FE-chips, but also different reset signals are generated. In case of overflowing buffers these reset signals are needed to avoid a wrong hit assignment due to timing errors.

$<sup>^{12}</sup>$ see figure 3.16

Figure 3.15.: Schematic drawing of the production steps for indium-bumps (left) and lead-tin-bump (right) [20].

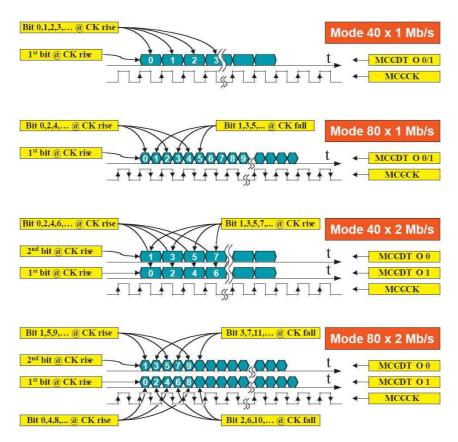

After a received Level1 trigger, the data from the FE-chips is read out into 16 FIFOs<sup>13</sup>. This whole data set is then combined to one event and furnished with a time stamp. Subsequently, the resulting data package is forwarded to the further read-out electronics as a serial data stream. Figure 3.16 shows a block diagram of the MCC, where the communication paths are highlighted in grey. The communication with the ATLAS data-taking system is realized via the "module port", which has three LVDS<sup>14</sup>-inputs and two outputs. The input lines are one data line (DCI) and two timing lines (CK and XCKIN), whereas the module port is synchronized using the CK timing line. The MCC has two data out lines, DTO and DTO2. The default speed per data line is 40 MBit/s. This speed can be increased to 80 MBit/s per data line by sending data not only at the rising edge of the 40 MHz cycle, but also on the falling edge. On top of that, both data lines can be used in parallel, which offers read-out speeds of 40 MBit/s, 80 MBit/s (either by using  $1 \times 80$  MBit/s or  $2 \times 40$  MBit/s) and 160 MBit/s (which means  $2 \times 80$  MBit/s). An illustration is given in figure 3.17.

All data received on the DCI-port is sent to the "command decoder", where it is in case of configuration data directly forwarded to the "Front End port". The Front End port has seven lines on which data is sent to the FE-chips and 16 differential ports for data read-out from the FE-chips (DTO0...DTO15). Out of the seven data lines to the chips, three simple lines are needed for module configuration (DAO, LD and CCK) and the other four (SYNC, LV1, STRB and XCK) are differential lines used for time critical operations such as trigger- and reset-signals.

Every time a Level1 command is sent to the MCC, a Level1 trigger is transmitted by the

<sup>&</sup>lt;sup>13</sup>First In, First Out; used as buffer

<sup>&</sup>lt;sup>14</sup>Low Voltage Differential Signalling

Figure 3.16.: Block diagram of the Module Control Chip [23].

command decoder to the TTC<sup>15</sup>. The TTC generates the L1 trigger for the Front End-chips upon reception of the Level1 command. It can also generate various reset signals for the MCC and the FE-chips, as well as calibration signals for the FEs. In case the number of events in the "PendingEvCnt" waiting for transmission to the off-detector read-out has reached 16, the generation of trigger signals is stopped and an error flag is set. If the number is lower than 16, a trigger is released and the number of bunch-crossings (BcoCnt) as well as the number of Level1 triggers (Lv1Cnt) in the "PendingLv1FIFO" is increased by 1. This information is later used for the event-building tasks of the MCC.

If a trigger has been transmitted to the FE-chips, all data belonging to this trigger is sent to the MCC in parallel, after which every chip sends an "End-Of-Fragment" word to signalize that the data set is complete. To store the data sets the MCC has 16 "Receiver Channels", one for every FE-chip and each equipped with a 128 words deep FIFO. After a Receiver Channel detects

<sup>&</sup>lt;sup>15</sup>Trigger, Timing and Control

Figure 3.17.: Possible read-out speeds supported by the MCC and the consequences for data encoding [22].

the End-Of-Fragment word, a signal is sent to the "EventScoreBoard" in the "Event Builder". As soon as all 16 channels show a detected End-Of-Fragment word in the EventScoreBoard the EventBuilder reads the data of the 16 Receiver FIFOs and the whole set is transmitted, together with the information stored in the PendingLv1FIFOs, to the data-out lines. Afterwards the FIFOs are reset.

The "RegisterBank" stores the internal configuration and status registers that are needed for the MCC operation.

The MCC also offers the possibility that artificial events together with a trigger are sent from the outside world (especially by a test driving operator) to the module port and are then written into the FIFOs. This causes the read-out chain to proceed in the way described above and the event is sent back. In chapter 5.3 one of the described measurements is based on exactly this feature, because it provides the chance to test the whole data-taking chain from beginning to end.

#### 3.5. Off Detector Read-Out

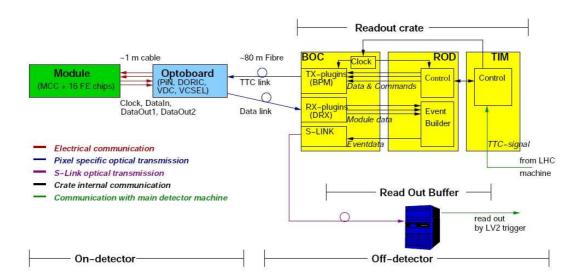

The long distance from the detector to the counting room combined with the high data rate require optical data transmission between the detector modules and the off-detector electronics. Consequently opto-electrical interfaces are needed on the on-detector part – the so called optoboards – as well as on the off-detector part, called Back of Crate card (BOC). They are connected via about 80 m long fibres. One fibre per module is needed for the data transfer from

Figure 3.18.: Schematic overview of the Pixel detector read-out chain [?].

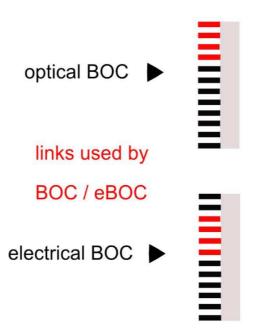

the off-detector electronics to the module, in particular for the clock and command signals. For the data transfer from the module to the off-detector electronics there is one fibre, or for the B-layer two fibres, needed per module. On the counting room side 1, 2 or 4 optoboards are connected to one BOC, depending on the chosen bandwidth. Every BOC is connected one-to-one to a Read Out Driver (ROD). All in all 132 BOC - ROD pairs are needed to read out the whole ATLAS pixel detector.

The ROD - BOC pairs are arranged in nine 9U VME crates. Each crate houses up to 16 of these card pairs and is controlled by a Single Board Computer (SBC). Via ethernet, the SBCs establish the connection to several computers that steer and control the data acquisition. On top of that every crate houses an interface card for distribution of (global) timing and trigger commands, sent by LHC control. This interface is called Timing and Control Interface Module (TIM). Figure 3.18 shows a schematic overview of the whole data read-out chain. As can be seen in this figure every BOC card has an optical data output to the Read Out Buffer (ROB), which is the data path during data-taking mode. In the following sections all the parts mentioned above are described in more detail.

### 3.5.1. Optoboard

There is always one half-stave or one sector of the pixel detector connected to one optoboard [12]. This means, that there are 6 or 7 modules connected to one optoboard, which is a compromise of two aims. On the one hand it is desired not to have too much material within the detector volume, on the other hand not to loose too many modules in case of a damaged optoboard.

The optoboards are beryllium-oxide printed circuit boards, every optoboard is mounted on the Patch Panel 0 (PP0) which establishes the connection to the modules. Each optoboard is featured with one 8-way PIN diode array and for the outer layers with one 8-way VCSEL array. For the B-layer two 8-way VCSEL arrays are applied to every optoboard to achieve a read-out speed of 160 MBit/s<sup>17</sup>. The two outer layers are read out at 80 MBit/s or 40 MBit/s, for which reason only one VCSEL array per optoboard is needed.

<sup>&</sup>lt;sup>16</sup>Vertical Cavity Surface Emitting Laser

<sup>&</sup>lt;sup>17</sup>running two data lines, each at 80 MBit/s

Figure 3.19.: The BeO based optoboard with one VCSEL array and one PIN diode array, as it is used for the two outer detector layers. The size of the optoboards is 2 cm  $\times 6.5$  cm.

All in all 272 optoboards are needed to read out the whole detector. The connection between optoboards and counting room is realized using optical fibres. Every fibre is ribbonized into 8-way ribbons. One ribbon is used to send the trigger, timing and command signals to the detector and for Layer 1 and Layer 2 on one ribbon the data from the detector to the counting room is sent. The B-Layer requires two ribbons to send its data to the counting room. Thereby each module has its own communication channels. The clock and command signals are encoded by the TX plug-ins into one BPM<sup>18</sup> signal, which is sent to the optoboard. This provides the combined information on one instead of two fibres, thus additional material within the detector volume is avoided. The combined signal is received by one PIN-diode per channel and afterwards decoded in a special ASIC, the DORIC<sup>19</sup>, which is explained in the following subsection. The DORIC provides separated electrical clock and command signals to the module.

In the opposite direction the MCC sends data electrically to the optoboard, where another ASIC, the VDC<sup>20</sup>, drives the VCSEL channel by channel. The data from one module is sent always on the same ribbon to the counting room. The data transfer is realized using a Non-Return-to-Zero (NRZ) signal.

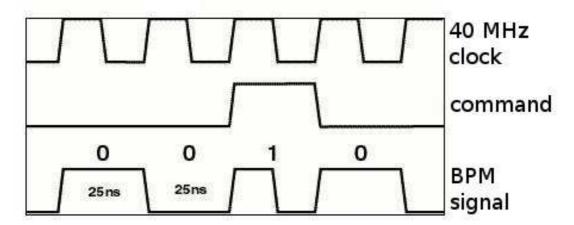

Figure 3.20 shows an example for a BPM-coded signal. The encoding of data streams into BPM signals provides a better clock recovery than data streams without an encoding scheme. In case the binary data stream is sent without modification, the result can be a long series of logical zeros or ones, if BPM encoding is not used. This leads to problems concerning clock recovery and synchronization. BPM encoding ensures at least one transition between every data bit, because the clock and the data signal are combined as shown in figure 3.20. Thus synchronization and clock recovery is much easier.

<sup>&</sup>lt;sup>18</sup>BiPhase Mark

<sup>&</sup>lt;sup>19</sup>Digital Opto-Receiver Integrated Circuit

<sup>&</sup>lt;sup>20</sup>VCSEL Driver Chip

Figure 3.20.: Principle of encoding a 40 MHz clock signal and a command signal into a BPM-signal.

#### **DORIC**

The PIN-diode receives optical signals and converts them into electrical signals. These signals are forwarded to the DORIC, which is a four channel chip. Its task is to decode the received BPM signals into separated clock and command signals. The input current has to be between 40  $\mu A$  and 1000  $\mu A$ . The allowed duty cycle for the reconstituted clock is  $(50 \pm 4)$ % with a timing error of less than 1 ns. After receiving a radiation dose of 50 Mrad the bit error rate of the DORIC has to be less than  $10^{-11}$ .

Since the signal that has to be decoded is a BPM signal, the clock looks like a 20 MHz clock in case of only zeros being decoded. This is always the case after the system has been powered up. Thus the DORIC has to be reset after power up to get reliably into the 40 MHz frequency. After the correct frequency is achieved, the 40 MHz clock is used as an input to a delay-lock loop. There the internal delays are adjusted until the desired 50% duty cycle is reached. In this operating mode the data recovery circuit is sensitive to the edges of the input signal. In case the recovered clock is "high" a data signal is recovered, for a "low" clock signal no data is recovered. This signal is synchronized to the recovered clock and then sent as an LVDS signal to the connected module.

#### VDC

The VDC converts the LVDS signals that are sent by the modules, into signals driving the VCSEL channels. The VDC also is a four channel chip, like the DORIC. The VDC's output current can be adjusted by an external control voltage. This voltage is converted into a control current and thus the control current can be varied between 0 mA and 20 mA. During operation the VCSEL is always kept at a minimum current of about 1 mA to increase the switching speed.

#### 3.5.2. Back of Crate card

On the off-detector side the Back of Crate Card (BOC) is the opto-electrical interface [12]. The BOC has been designed for the SCT as well as the pixel detector. For both detectors the layout is the same, just the number of used channels differs. While every BOC that is used in the SCT read-out chain always handles 48 modules, a BOC in the pixel detector read-out is connected

to 6 or 7 B-Layer modules, 12 disk modules, 13 Layer 1 modules or 26 Layer 2 modules. The different numbers of connected modules are due to the different bandwidths used.

The BOC provides the complete timing functionality for the pixel detector. The Back of Crate card is – as the name indicates – located on the back side of the read-out crates used for the ATLAS pixel detector. As previously mentioned, all in all 132 BOC cards are needed

Figure 3.21.: Back of Crate card in pixel configuration [12].

for the pixel detector. Each BOC is connected to a ROD<sup>21</sup>. The BOC provides the interface between ROD and on-detector electronics, as well as to the Read Out Buffers (ROB). Since the module data received on the BOC is forwarded to the ROD, the number of connectable modules depends on the bandwidth of the ROD. This leads to a maximum number of 32 connectable pixel modules, whereas due to modularities not all available channels are used and thus only up to 26 modules are connected. The following list contains the main tasks for the BOC:

- Reception and distribution of the clock signal provided by the TIM.

- Reception of the electrical control signals for the modules that are sent by the ROD. These signals are converted into BPM-encoded optical signals and fed into the laser plug-ins.

- For the transmitted signals several adjustment functions, such as masking, timing and laser current adjustment, are provided.

- For the received data a timing and threshold adjustment for the PIN diode and a clock synchronization are provided.

- The data streams of Layer 1 modules and B-Layer modules are demultiplexed from 80 MBit/s per data line to 2 × 40 MBit/s.

- The optical signals containing the modules' data packages that are sent by the optoboard are received, converted into electrical signals and forwarded to the ROD.

- The parallel event data stream is received from the ROD and sent to the Read Out Buffer (ROB) via S-link.

- An off-detector laser safety interlock is provided.

<sup>&</sup>lt;sup>21</sup>see section 3.5.3

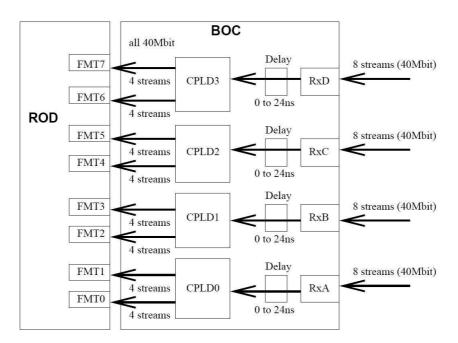

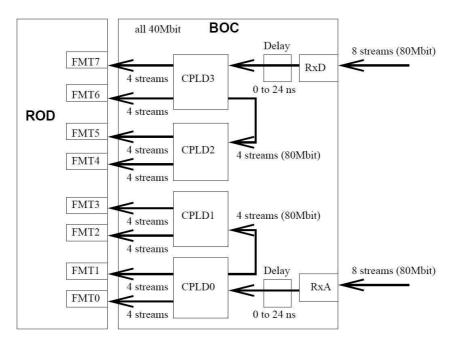

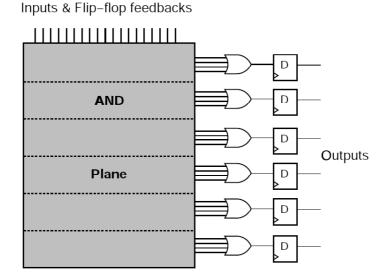

The BOC card can be divided into functional blocks, the clock section, the transmission section, the data receive section and the S-link section. The main functions on the BOC are performed by seven CPLDs<sup>22</sup>. The communication with the ROD and the main control of the BOC is provided by one CPLD, two are used for the communication with the transmitting (TX) and receiving (RX) plug-ins and four are controlling the receiving section, splitting of data streams for high bandwidth modes and registration of data.

#### **Clock Section**

All BOCs in a crate receive the 40 MHz system clock from one Timing, Trigger and Control Interface Module (TIM). On every BOC, this clock signal is multiplexed into five clocks, one of which is transmitted directly to the ROD. Another one – the BPM- or P-clock – is passed to the transmission section and thus to the modules. For the BOC internal chip functionality another clock is used, the A-clock. The remaining two clocks, the B-clock and the V-clock, are used for data recovery. As previously mentioned, some of the clocks are adjustable. The P-clock can be delayed by 0 ns up to 24 ns in 1 ns steps to adjust the timing of the modules. The same range is available for the B-clock, which is the clock for normal data recovery. For data recovery in 80 MBit/s mode the V-clock is used. This clock can be delayed coarsely from 0 ns up to 49 ns in 1 ns steps and additionally from 0 ns up to 10.2 ns in 40 ps steps. A summary of the timing capabilities is given in table 3.3.

| clock signal | purpose                                        | delay capability                 |

|--------------|------------------------------------------------|----------------------------------|

| system clock | received from the TIM                          | none                             |

| A-clock      | for BOC-internal chip functionality            | none                             |

| P-clock      | encoded together with command signals for the  |                                  |

|              | modules into BPM signal                        | 0  ns to  24  ns, 1  ns steps    |

| B-clock      | normal data recovery clock                     | 0  ns to  24  ns, 1  ns steps    |

| V-clock      | data recovery clock for 80 MBit/s mode         | 0  ns to  49  ns, 1  ns steps    |

|              |                                                | 0  ns to  10.2  ns, 40  ps steps |

| ROD-clock    | clock transmitted to ROD, copy of system clock | none                             |

Table 3.3.: Clock signals and their adjustment ranges used on the BOC.

#### **Transmission Section**

The commands for the modules are sent from the ROD to the transmission section of the BOC. In the transmission section four TX plug-ins are located. Every TX plug-in houses an 8-way VCSEL array and a BPM chip where data and clock signals are encoded into the BPM signal. Each plug-in has an 8-way fibre ribbon connected, which establishes the connection to one optoboard. Figure 3.22 shows a TX plug-in.

The transmission section provides several tuning capabilities. For every TX plug-in the delayable P-clock is multiplexed for all module channels. The BPM-chip offers an additional tunable delay for each channel individually. This delay can be set using a fine delay for 0 ns up to 35.56 ns in 280 ps steps as well as by a coarse delay for values from 0 ns up to 775 ns in 25 ns steps. Thus every module timing can be tuned individually with respect to the bunch crossing timer. Additionally the TX laser output power, the mark-to-space ratio of the BPM signal and

<sup>&</sup>lt;sup>22</sup>Complex Programmable Logic Device

Figure 3.22.: TX plug-in with a size of 1.5 cm  $\times 3.5$  cm, which encodes the BPM signal and transmits it to the optoboard [12].

an inhibit signal to block the BPM encoding of the data can be adjusted. An overview of the parameters is given in table 3.4.

| parameter            | range                          | purpose                          |

|----------------------|--------------------------------|----------------------------------|

| BPM inhibit          | on/off                         | prohibits BPM encoding of data   |

| BPM fine delay       | 0 ns to 35.56 ns, 280 ps steps | channelwise settable delay       |

|                      |                                | for data stream to module        |

| BPM coarse delay     | 0 ns to 775 ns, 25 ps steps    | channelwise settable delay       |

|                      |                                | for data stream to module        |

| BPM mark-space-ratio | settings 0 to 31               | adjustment of signal mark space  |

|                      |                                | from 30:70 to 70:30              |

| laser current        | settings 0 to 255              | sets the laser current to values |

|                      |                                | between 0 mA and 18 mA           |

Table 3.4.: Tunable parameters of the BOC's transmission section and their ranges.

#### Receiver Section

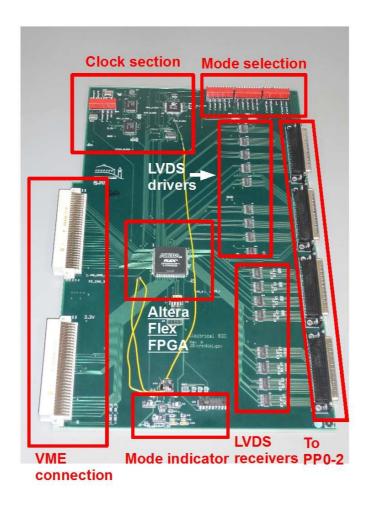

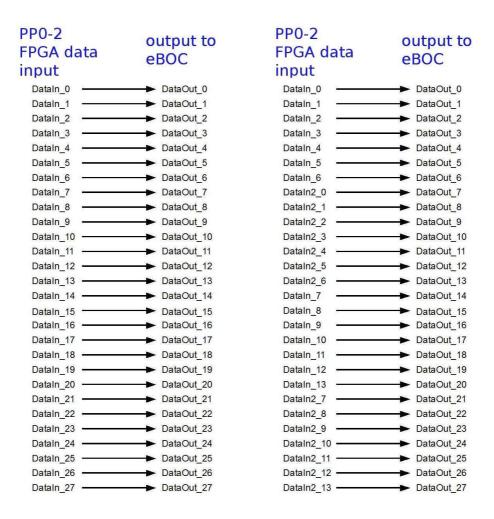

The receiver section of the BOC card is treated in more detail, since the same data management that is used on the optical BOC's FPGA had to be implemented to the eBOC.

In the receiver section the module data, sent by the optoboard, arrives on the RX plug-ins. Every pixel BOC card can serve up to four RX plug-ins, each of which provides eight channels. Thus up to 32 modules can be connected to each BOC. The main parts of a RX plug-in (see figure 3.23) are an 8-way PIN diode array, which is the converter from optical to electrical signals, and an amplifier chip. The amplifier chip uses eight channels, although it has twelve, which are used for SCT read-out. For every RX channel the threshold can be controlled to ensure a reliable differentiation between "0"s and "1"s. The received electrical signals are amplified and sent differentially to the BOC card. There the signals are synchronized to the ROD clock and transmitted as 40 MBit/s streams. The delay needed for synchronization can be varied between 0 ns and 24 ns in steps of 1 ns for every stream.

The receiver section houses four CPLDs, one for every RX plug-in. In the CPLDs the received data is registered and clocked out with the B-clock, which provides a stable phase to the ROD clock.

Figure 3.23.: RX plug-in with a size of 1.5 cm  $\times$ 3.5 cm, which transforms the received optical signals into electrical and passes them to the BOC [12].

Since the ROD only accepts data streams at 40 MBit/s the CPLDs have another functionality for data received at 80 MBit/s (Layer 1) or 160 MBit/s (B-Layer). Every 80 MBit/s stream is demultiplexed into two streams, each at 40 MBit/s. The 160 MBit/s mode is treated identically, since it corresponds to  $2 \times 80$  MBit/s.

Because the number of used streams doubles in case of switching from 40 MBit/s to 80 MBit/s and quadruples at switching from 40 MBit/s to 160 MBit/s, the number of connectable modules decreases. Thus at 80 MBit/s two TX plug-ins and two RX plug-ins are used on one BOC and at 160 MBit/s one of each is used.

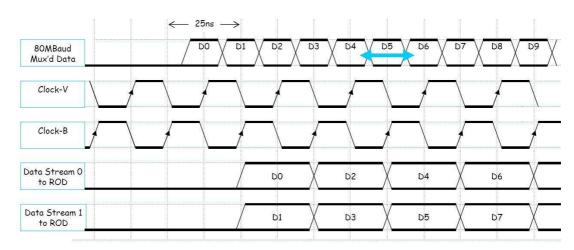

For the demultiplexing of 80 MBit/s streams into 40 MBit/s streams both recovery clocks – B-clock and V-clock – are used. One 40 MBit/s stream is generated reading every second bit of the faster stream and another 40 MBit/s stream is generated reading the other bits. For generation of the first stream the B-clock is used, for the second stream the V-clock is used, which is opposite to the B-clock. This principle is illustrated in figure 3.24.

Figure 3.24.: Demultiplexing an 80 MBit/s stream into two 40 MBit/s streams with respect to the two recovery clocks [24].

A small routing board is located between the four CPLDs processing the received data to have a balanced work load even in case of less than four used RX plug-ins. Thus the complete

data line sorting can be done on the BOC card. All available tuning parameters of the receiving section are shown in table 3.5. In summary, the data flow through the BOC at 40 MBit/s is shown in figure 3.25 and at 80 MBit/s or 160 MBit/s in figure 3.26.

| parameter          | range                        | purpose                                                    |

|--------------------|------------------------------|------------------------------------------------------------|

| RX threshold       | settings 0 to 255            | channelwise threshold, range from 0 $\mu A$ to 250 $\mu A$ |

| RX data delay      | 0 ns to 25 ns, 1 ns steps    | channelwise adjustment of the data phase                   |

| B-clock            | 0 ns to 25 ns, 1 ns steps    | global clock for data sampling to the ROD                  |

| V-clock            | 0 ns to 25 ns, 1 ns steps    | additional demultiplexing clock                            |

| V-clock fine phase | 0 ns to 10.2 ns, 40 ps steps | V-clock fine adjustment                                    |

Table 3.5.: Receive section parameters of the BOC card [12].

Figure 3.25.: Data routing through the BOC in 40 MBit/s mode [12].

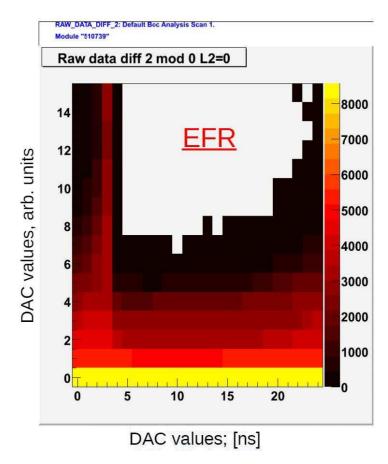

Altogether it requires quite a long tuning procedure to attune all optical components to each other and reach a reliable state. One of these steps is the BOC scan. This scan determines the best working point for the optical data link. A predefined bit pattern is sent to the modules and passed back to the ROD. Afterwards the number of bit flips is colour coded in a 2-dimensional histogram, where an example is shown in figure 3.27. The position of the error free region is determined and thus the optimal combination of receiver delay and receiver threshold can be set. These values depend on the temperature and the laser power of the optoboard.

#### S-Link Section and Further Functionalities

Every BOC card carries the S-Link card, or HOLA<sup>23</sup>, for sending out the data to the Read Out Buffers (ROB). It connects BOC and ROB using a parallel 32 bit connection at 40 MHz.

<sup>&</sup>lt;sup>23</sup>High speed Optical Link for ATLAS

Figure 3.26.: Data routing through the BOC in 80 MBit/s or 160 MBit/s mode [12].

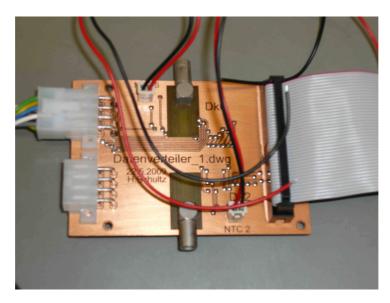

The BOC card provides some monitoring functions for its hardware. The supply voltages and currents of the PIN-diodes on the RX plug-ins can be read out as well as the temperatures of the TX and RX plug-ins can be measured using NTCs<sup>24</sup>.

Due to safety reasons the BOC card has to turn off the TX lasers in case of work going on close to them. Therefore two interlock lines are implemented into the system. These interlock lines are "AND"ed together, thus the lasers only work in case both lines are switched to the "laser on" state. The reason for two lines is that one interlock is located at the crates, where the TX plug-ins are located and the other one is connected to the on-detector laser interlock system. Thus safety is provided in case work is going on at the crates as well as for the case work is done at the on-detector side of the optical fibres, near the optoboards.

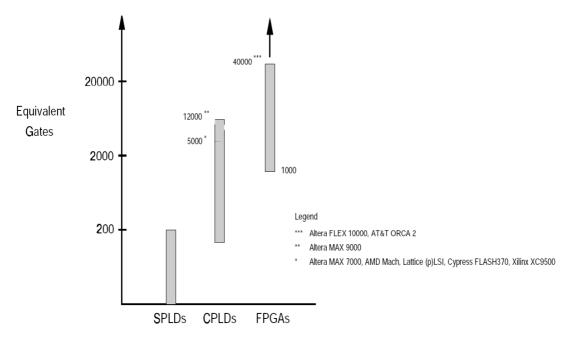

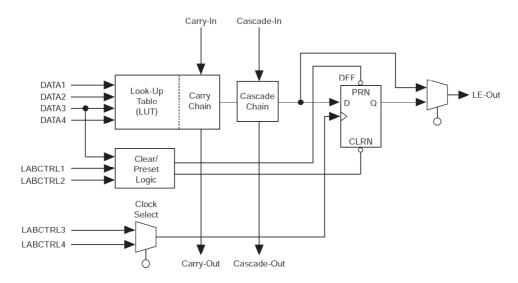

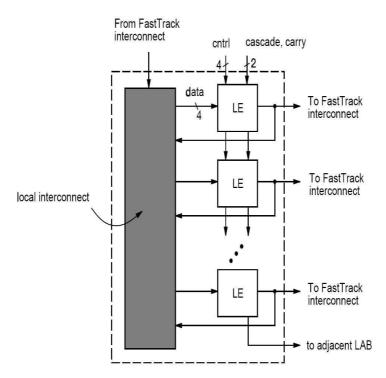

#### 3.5.3. Read Out Driver

The Read Out Driver (ROD) is, like the BOC, common for SCT and pixel configuration [19]. All main functions of the ROD are performed by FPGAs<sup>25</sup> and DSPs<sup>26</sup>. The firmware running on the RODs differs for SCT and pixel mode.

The main functions of detector control and read-out are provided by the ROD. Triggers received from the TIM are transmitted to the modules by the ROD, it generates the commands for the modules, transmits them to the BOC and is responsible for the formatting of event data received from the modules. Additionally, it provides several monitoring capabilities. Thus the ROD is not only essential for the detector in data-taking mode, but also for detector calibration and testing.

In data-taking mode trigger signals are received from the TIM and directly transmitted to the modules. The event data is processed in the ROD data-path and transmitted via S-Link to

<sup>&</sup>lt;sup>24</sup>Negative Temperature Coefficient resistors

<sup>&</sup>lt;sup>25</sup>Field Programmable Gate Arrays, see section 4.1

<sup>&</sup>lt;sup>26</sup>Digital Signal Processors

Figure 3.27.: The BOC scan determines the best working point for the optical data link, whereas the plot shows receiver delay vs. receiver threshold. The number of bit flips is colour coded.

the Read Out Subsystem (ROS). In calibration mode the triggers are generated by the ROD and histogramming and data processing is done on the four Slave DSPs located on the ROD.

The ROD can be separated into several functional regions. They are explained in the following subsections.

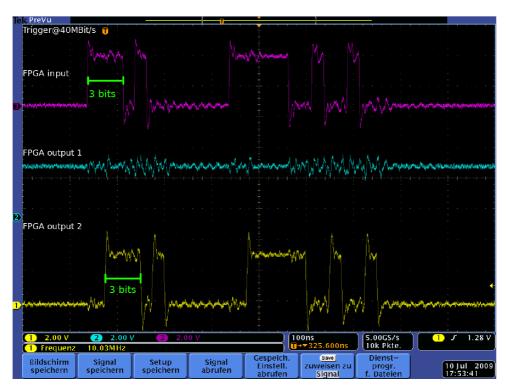

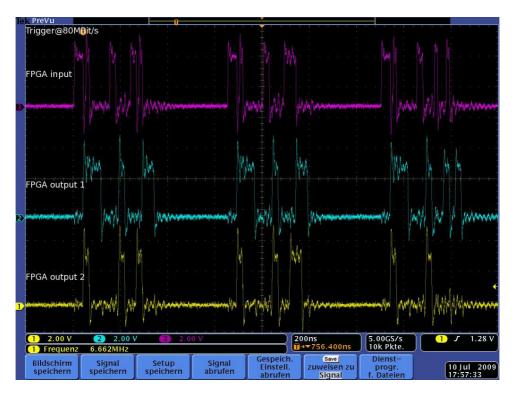

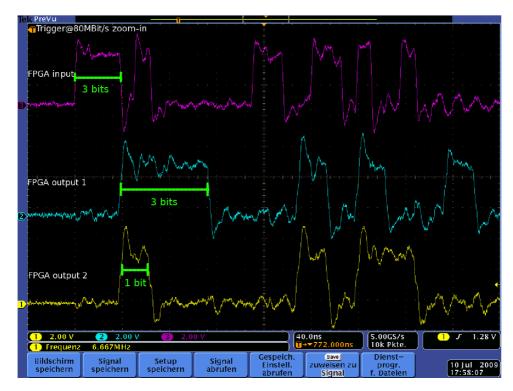

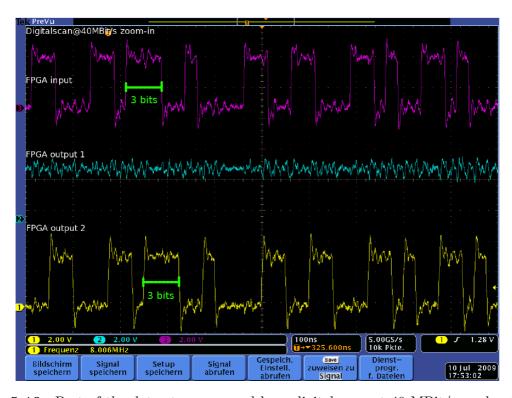

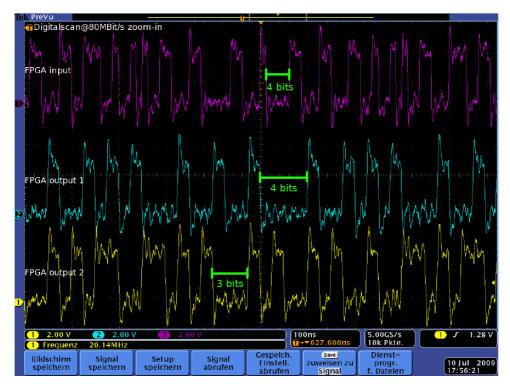

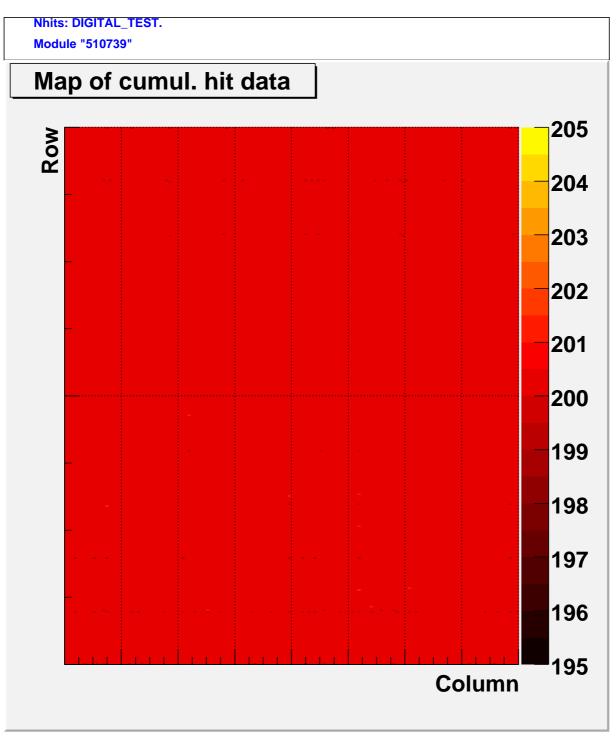

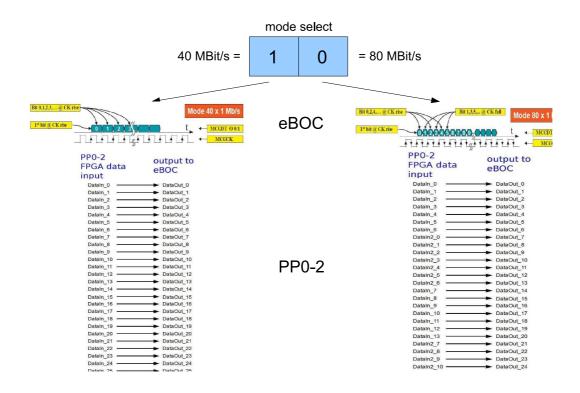

#### Controller FPGA and Master DSP